模拟集成电路设计流程--ESD保护电路和PAD电路

来源:IC Skill Porter

今天给大家分享模拟集成电路设计中ESD保护电路和PAD电路的内容。

常用的ESD保护电路

ESD保护电路设计中的注意事项,以及设计过程、仿真方法等,一般由专门的ESD完成设计工程师。布局也需要特别考虑。 ESD设计理论的内容在此不再赘述。有兴趣的同学可以自行学习ESD保护电路设计和器件原理。

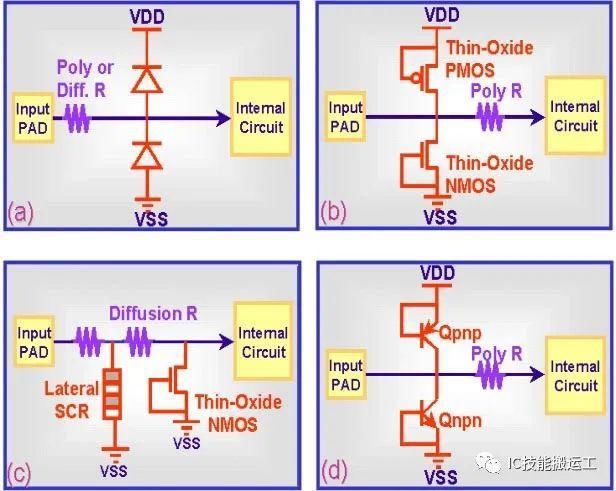

以下几种常用的ESD电路原理图(来自台湾交大课件)作为演示,详细学习可参考台湾交大课件。

上图(a)是最常见的ESD保护电路,在很多场合都见过;图(b)是CMOS工艺中最常见的ESD保护电路。这种连接称为GGNMOS(Gate Grounded NMOS),它使用寄生BJT来实现ESD保护;图(c)采用晶闸管实现ESD保护功能;图(d)与图(b)的原理是一致的。

上图(a)是最常见的ESD保护电路,在很多场合都见过;图(b)是CMOS工艺中最常见的ESD保护电路。这种连接称为GGNMOS(Gate Grounded NMOS),它使用寄生BJT来实现ESD保护;图(c)采用晶闸管实现ESD保护功能;图(d)与图(b)的原理是一致的。

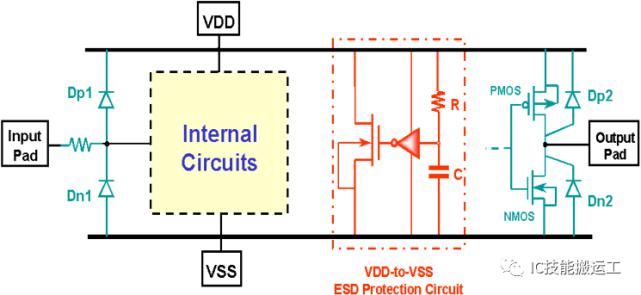

除了I/O中的ESD保护电路外,电源和地也需要相应的保护电路。电源和地之间需要一个钳位电路。为了安全起见,GGNMOS 也会被用作保护。

上图是一种全芯片ESD保护电路。红色虚线表示电源钳位电路。设计需要根据具体的ESD要求选择RC网络的时间常数和ESD放电管的尺寸。

上图是一种全芯片ESD保护电路。红色虚线表示电源钳位电路。设计需要根据具体的ESD要求选择RC网络的时间常数和ESD放电管的尺寸。

上述电路中使用的器件都是专用的ESD器件。通常 PDK 还应包括 ESD 设计特定的设备。这些器件经过处理以实现 ESD 保护功能。与非 ESD 器件相比,具有更好的 ESD 抗性,并且仿真模型会与普通器件不同。

ESD保护电路的布局

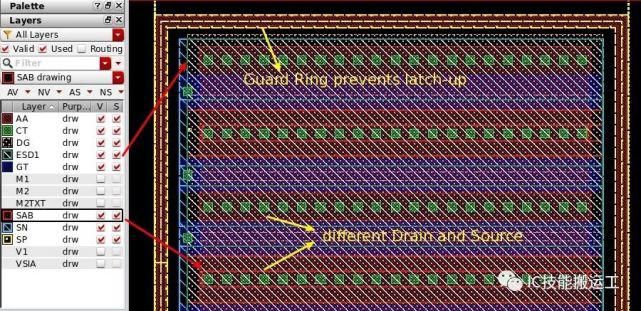

如果使用的PDK中没有特殊的ESD器件,则需要特别注意电路布局设计。 ESD器件在加工过程中与普通逻辑器件不同。有些工艺不同,所以工艺层数比逻辑器件多,需要在版图设计中加以考虑。

以上是小木同学在使用过程中用于ESD保护的NMOS实现所需的版本层.不同的进程可能有不同的实现方法,在一些进程中,还可以增加一个标识层来实现LDD进程。

以上是小木同学在使用过程中用于ESD保护的NMOS实现所需的版本层.不同的进程可能有不同的实现方法,在一些进程中,还可以增加一个标识层来实现LDD进程。

由于ESD器件的尺寸非常大,很容易造成闩锁。为了防止闩锁的发生,单个ESD器件的尺寸有一定的限制,最好加 使用有效的隔离环,或者使用隔离井将ESD器件放置在单独的井中.

I/O ESD 电路

I/O ESD 电路

电源钳位电路

电源钳位电路

放置在PAD环中的ESD保护电路

放置在PAD环中的ESD保护电路

上下滑动查看更多内容!

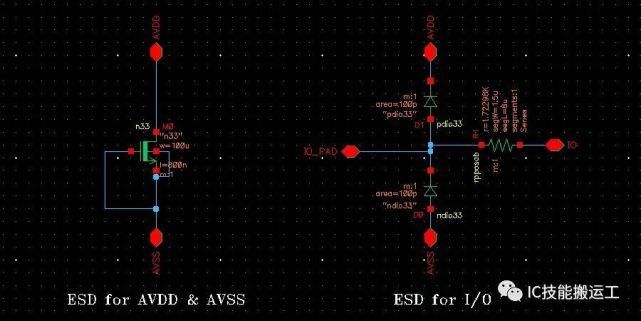

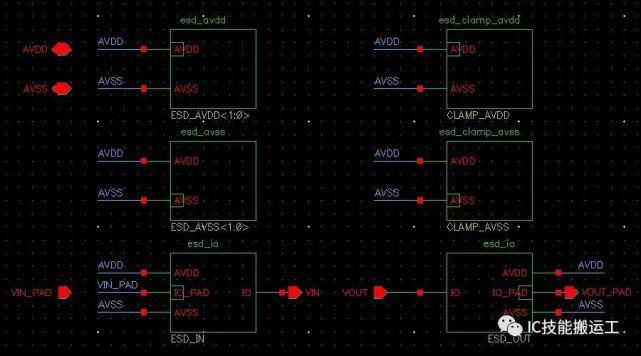

上图是小木设计的简单ESD电路图,作为演示。 ESD保护电路在电路设计时分为PAD Ring模块。该模块包含与 PAD 相关的所有电路设计。在版图上,这部分包括芯片供电网络的设计和封装方式的考虑。

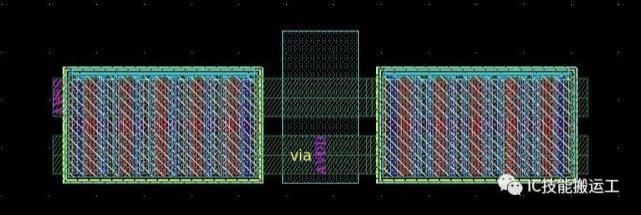

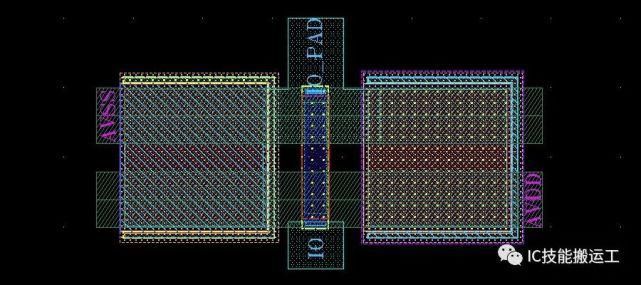

下图是对应示意图的布局部分。由于时间问题,电源钳位电路的布局没有给出具体的实现。与其他电路基本相同。您只需要注意ESD放电路径的规划。而已。

AVDD的ESD保护电路

AVDD的ESD保护电路

AVSS ESD保护电路

AVSS ESD保护电路

I/O ESD保护电路

I/O ESD保护电路